Authors: Qiang Wu, Yanli Li, Yushu Yang et al.

Institution:Shanghai IC R, &, D Center, 497, Gaosi Road, Zhangjiang Hi, -, Tech Park, China

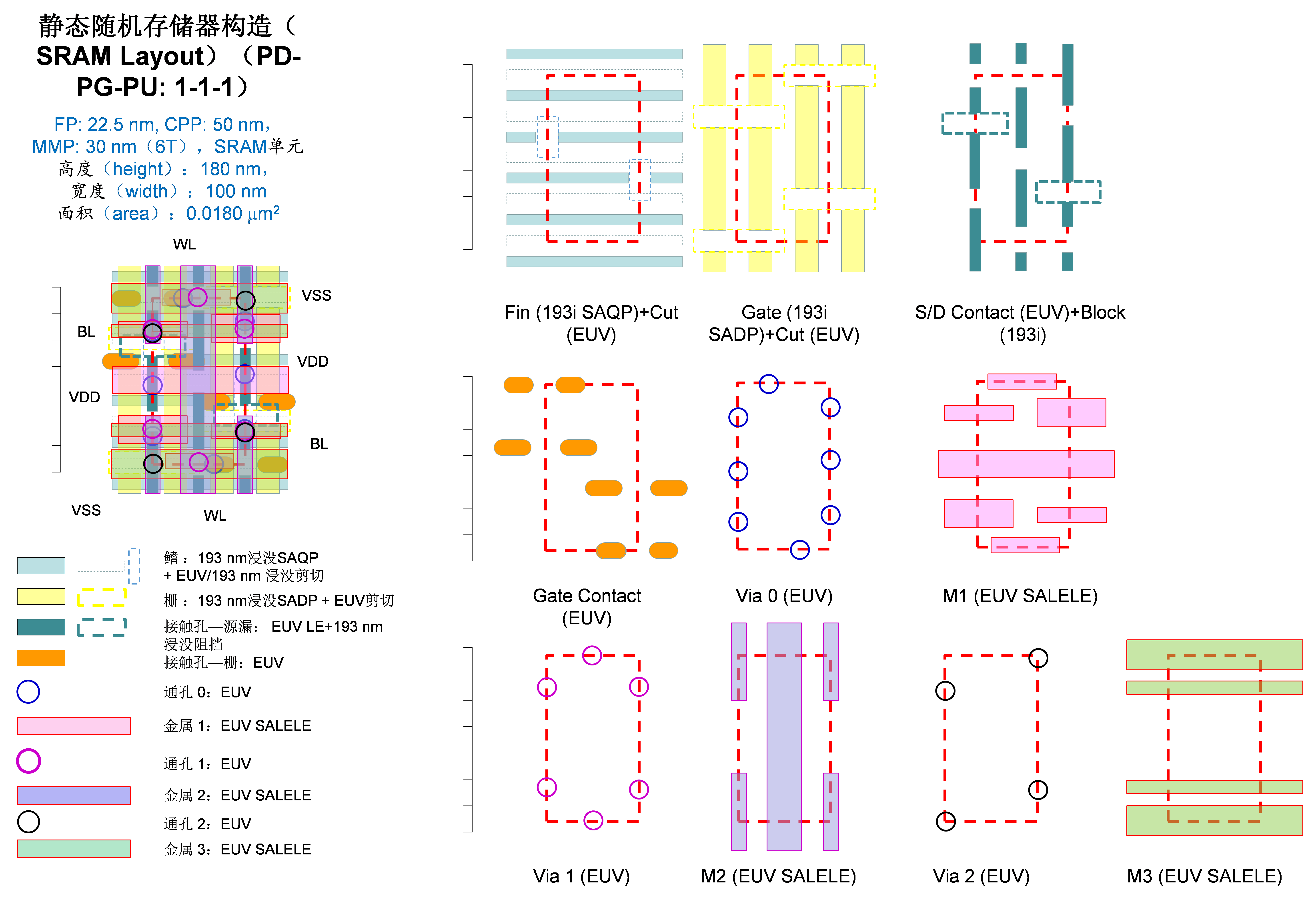

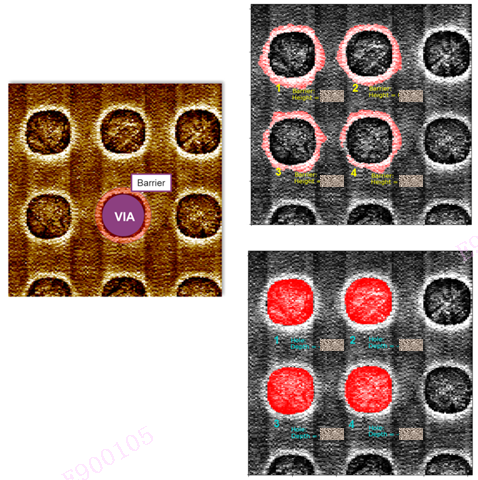

Keywords:5 nm Logic Process;EUV;SADP;self-aligned LELE;RCWA;stochastics;mask 3D scattering

doi:10.33079/jomm.19020408