Authors: Lihong Liu, Thierry Engel, Huwen Ding et al.

Institution:Institute of Microelectronics, Chinese Academy of Sciences, Beijing

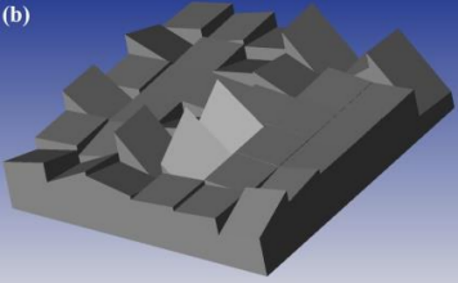

Keywords:Incoherent beam shaping;micro lens array;custom optimization

doi:10.33079/jomm.21040401

Abstract:

A reflective faceted structure is proposed to reshaping an incoherent light beam into two focalized spots. To obtain the desired irradiance distribution on a detector, custom optimization function ...

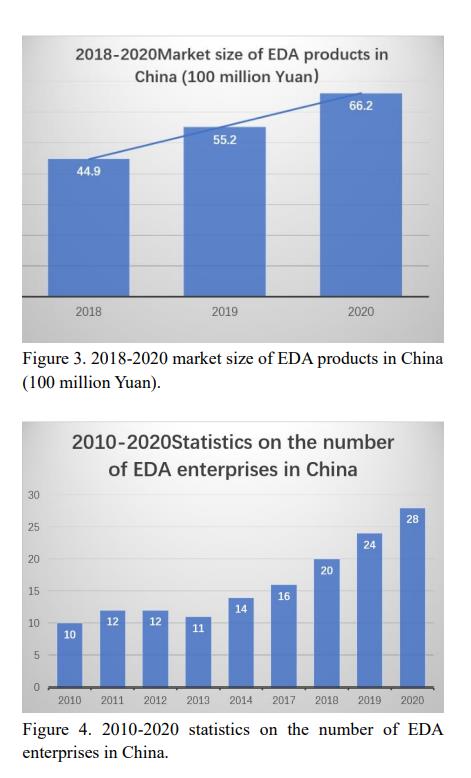

Keywords:EDA

doi:10.33079/jomm.21040302

Abstract:

China's IC industry has been flourishing in recent years, huge market demand together with government investments are the major driving forces for this development. The status and development momen...

Authors: Chang Xu

Institution:Fujian Jinhua Integrated Circuit Co, ., Ltd, ., Jinjiang, Quanzhou, Fujian

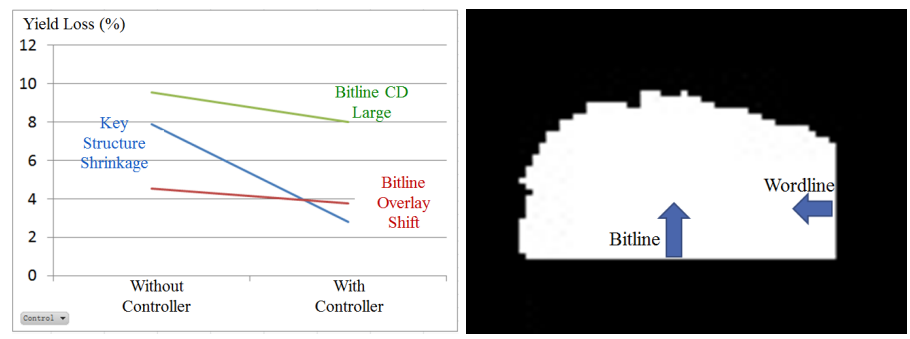

Keywords:R2R;manufacturing;control;circuit design;virtual metrology

doi:10.33079/jomm.21040301

Abstract:

This paper presents an innovative R2R (run to run) control strategy. This novel approach has made use of circuit design structure through virtually put up the structure before reach the actual stru...

Authors: Mark Neisser

Institution:Tan Kah Kee Innovation Laboratory

Keywords:Stochastics;Self-assembly;overlay;edge placement error;self-organizing;DNA origami;bottle brush polymers

doi:10.33079/jomm.21040202

Abstract:

Decades of progress in the semiconductor industry has led to lithographically printed dimensions that are small enough that the positions of individual molecules and the stochastic variation in the...

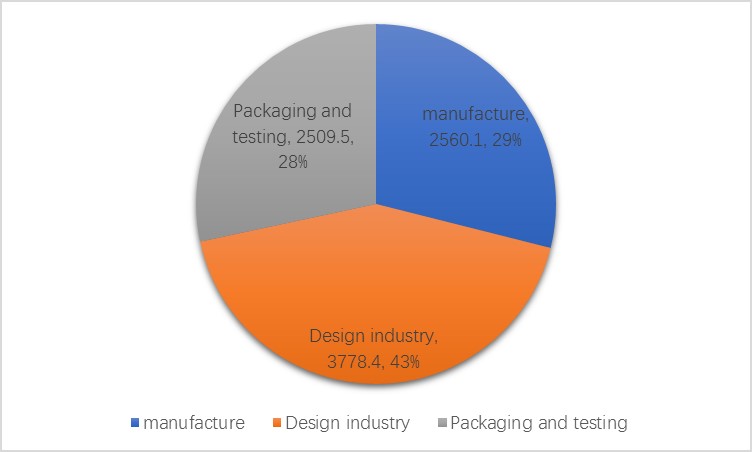

Keywords:IC industry; Integrated Circuit Design Market

doi:10.33079/jomm.21040203

Abstract:

China's IC industry has been flourishing in recent years, huge market demand together with government investments are the major driving forces for this development. The status and development momen...

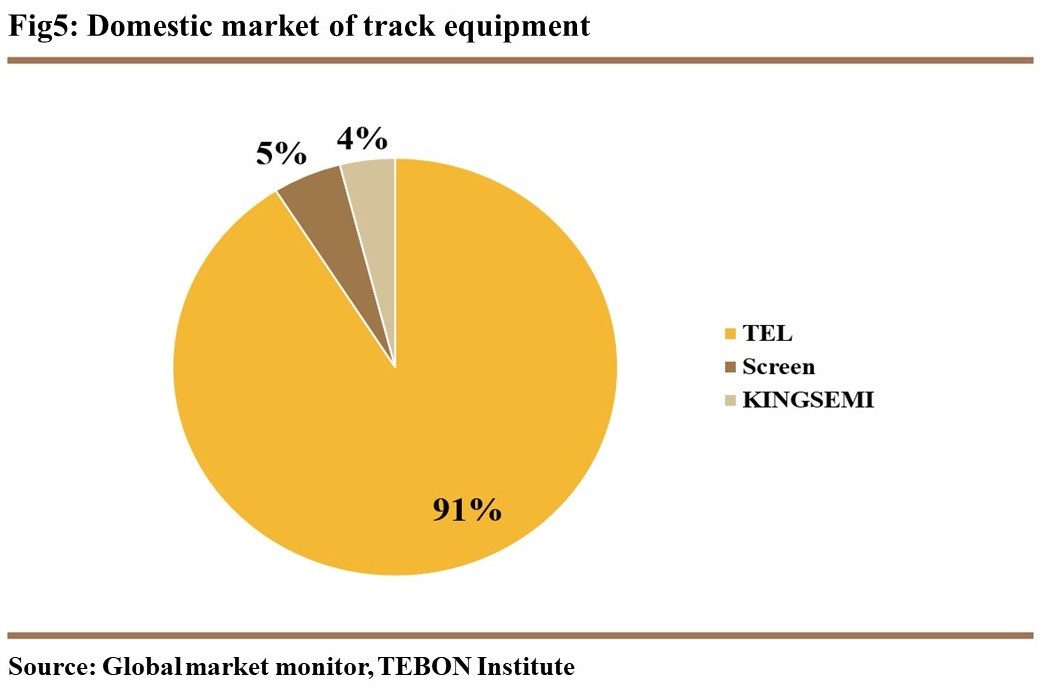

doi:10.33079/jomm.21040103

Abstract:

China's IC industry has been flourishing in recent years, huge market demand together with government investments are the major driving forces for this development. The status and development momen...

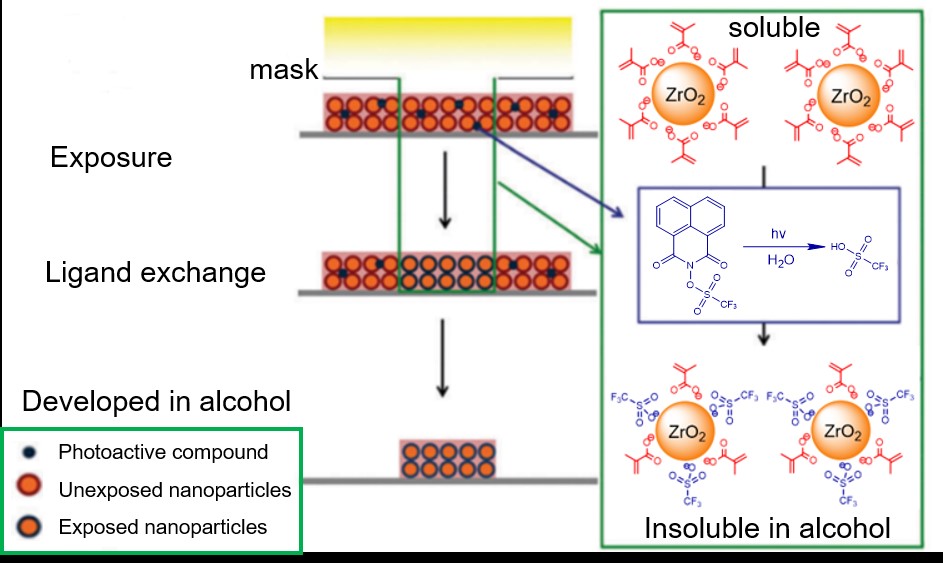

Authors: Zhihao Wang, Xindi Yao, Huiwen An et al.

Institution:Key Laboratory of Photochemical Conversion and Optoelectronic Materials, Technical Institute of Physics and Chemistry, Chinese Academy of Sciences, China

Keywords:Organic-inorganic hybrid photoresist;EUV lithography;nanocluster;nanoparticle;organometallic complex

doi:10.33079/jomm.21040101

Abstract:

Photoresists are radiation-sensitive materials used for forming patterns to build up IC devices. To date, most photoresists have been based on organic polymers, which have been dominating the semic...

Authors: Tao Zhou, Xuelong Shi, Chen Li et al.

Institution:Shanghai Integrated Circuits R, &, D Center Co, ., Ltd, ., Shanghai

Keywords:SEM images;contour extraction;machine leaning (ML);deep convolution neural network (DCNN);edge placement variation

doi:10.33079/jomm.21040102

Abstract:

Scanning electron microscope (SEM) metrology is critical in semiconductor manufacturing for patterning process quality assessment and monitoring. Besides feature width and feature-feature space dim...

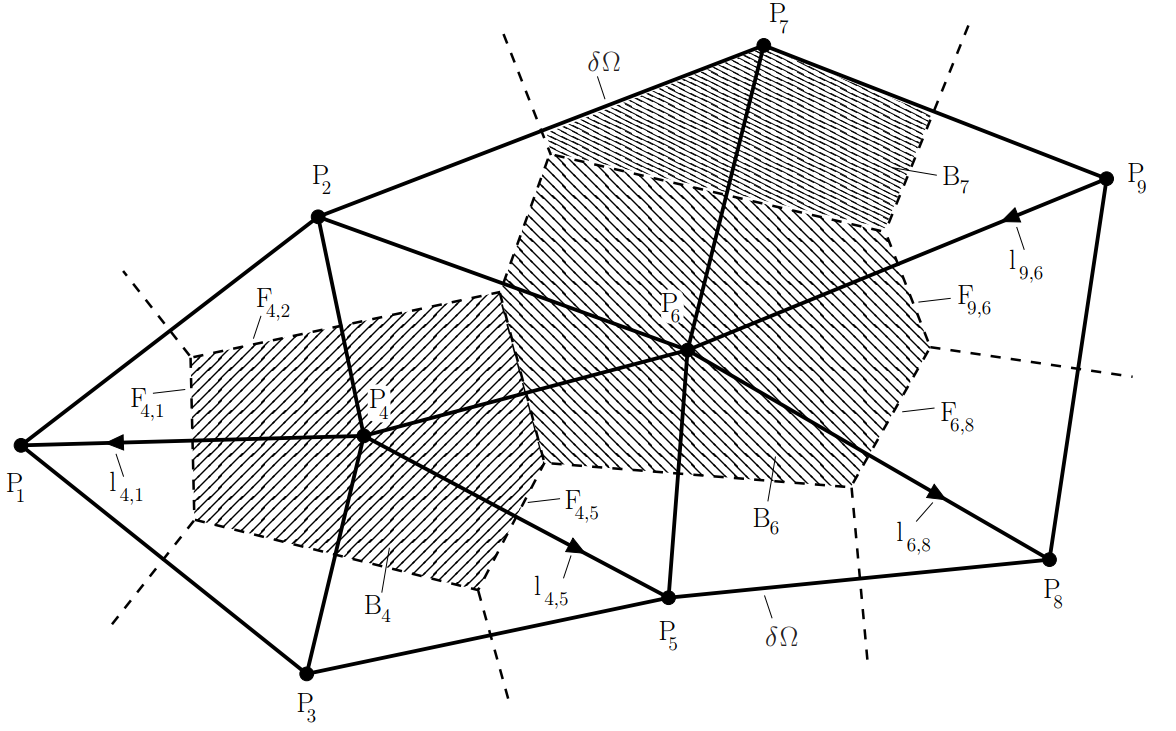

Authors: Bernd Meinerzhagen

Institution:Technical University Braunschweig

doi:10.33079/jomm.20030403

Abstract:

In 1964 Hermann Gummel published the first numerical solution method for the one-dimensional Drift Diffusion model. In his seminal paper [1] already the nonlinear iteration method and th...