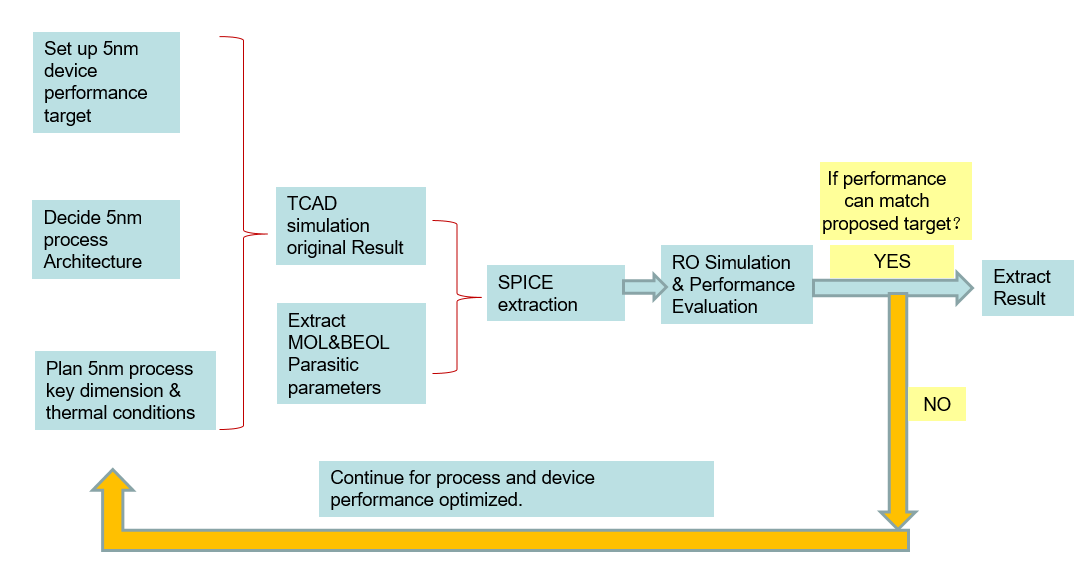

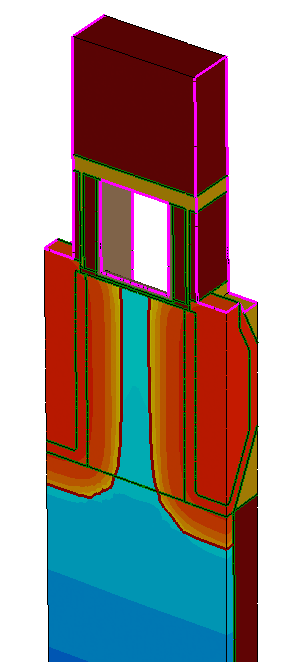

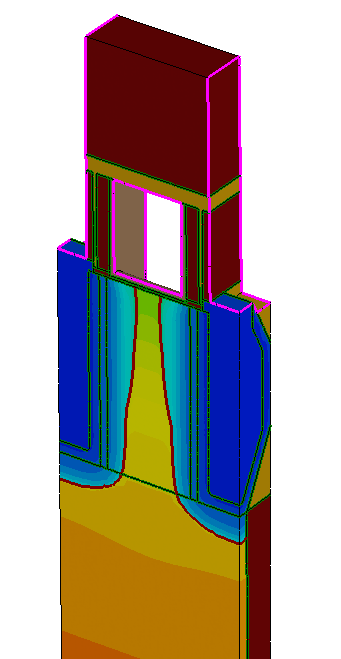

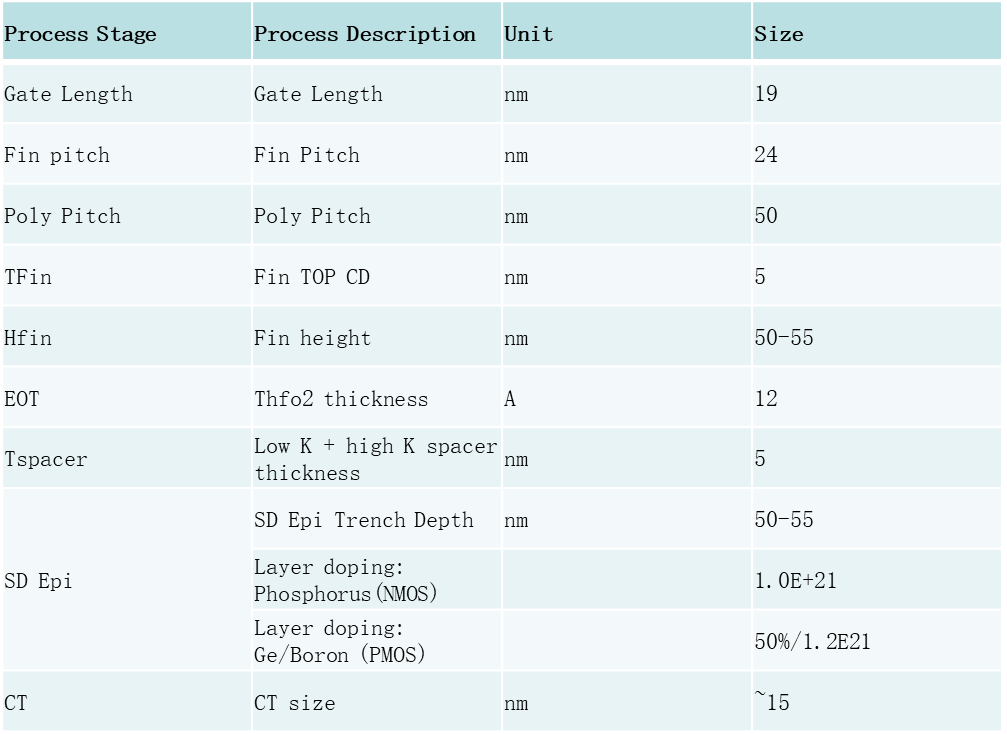

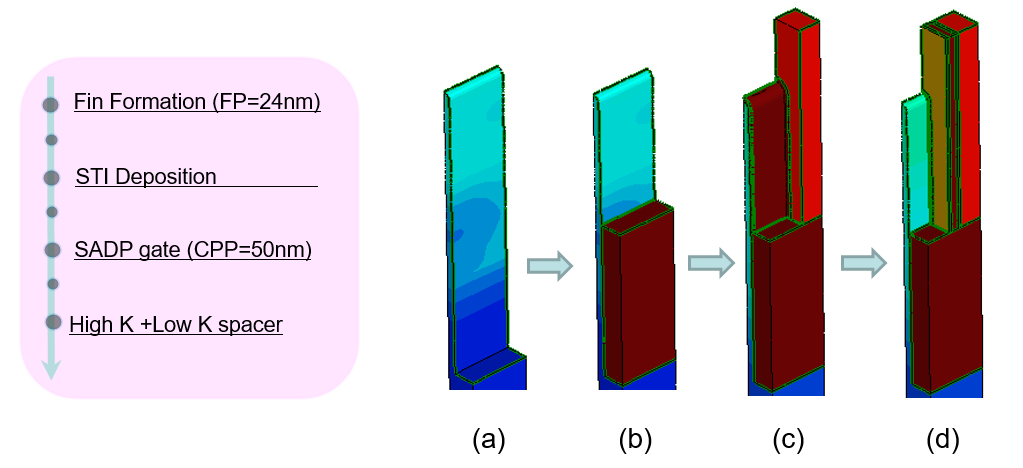

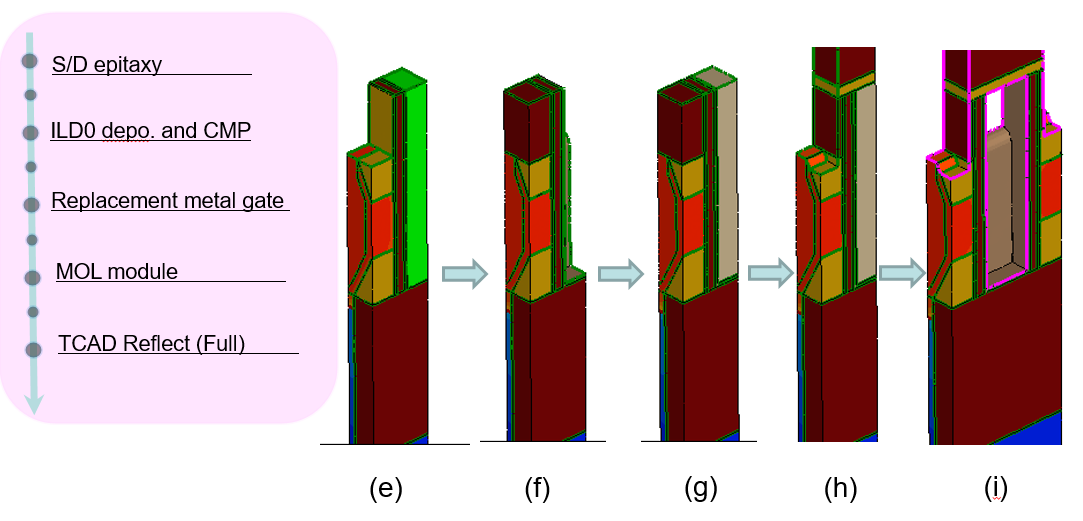

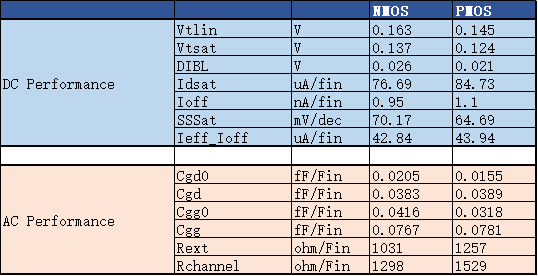

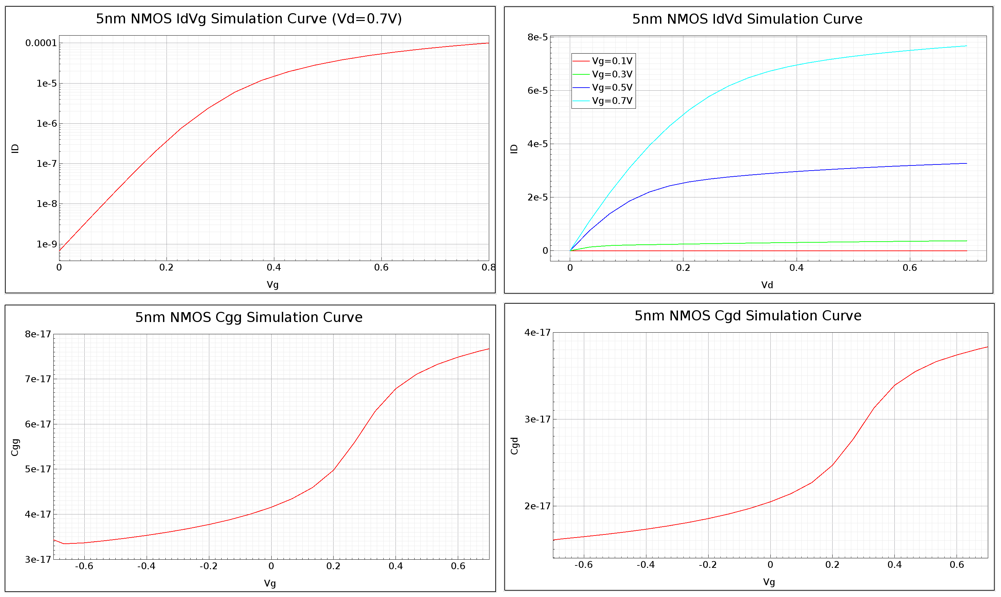

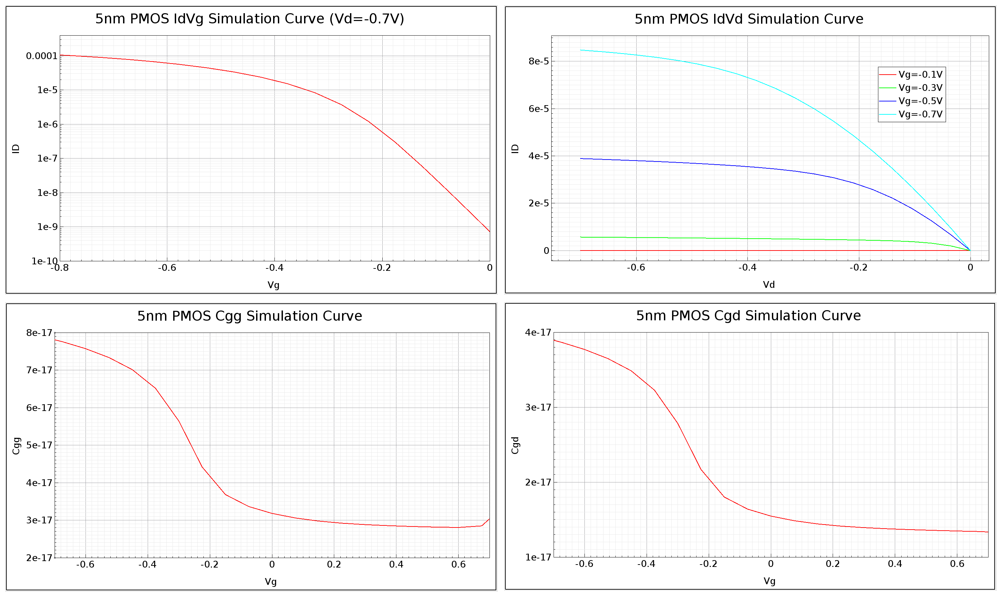

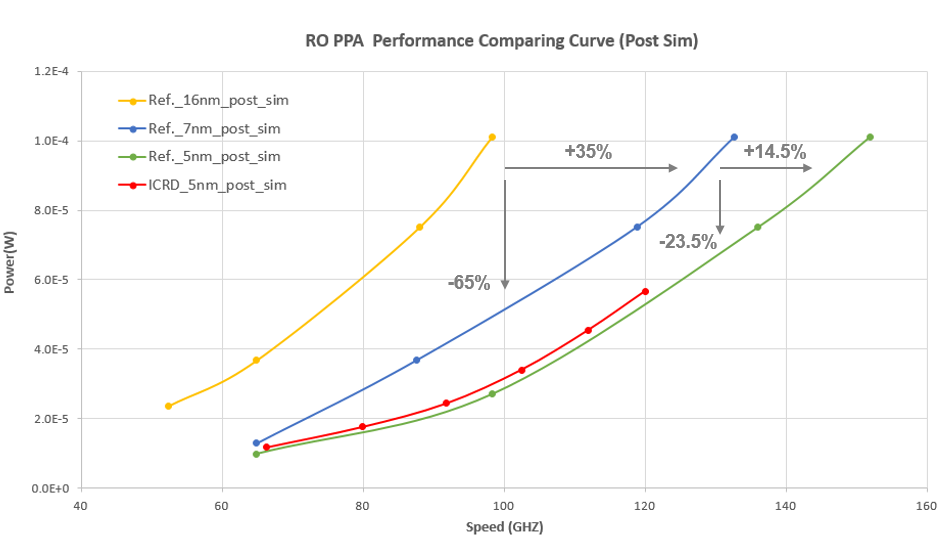

Abstract: With the continuous scaling in conventional CMOS technologies, the planar MOSFET device is limited by the severe short-channel-effect (SCE), Multi-gate FETs (MuG-FET) such as FinFETs and Nanowire, Nanosheet devices have emerged as the most promising candidates to extend the CMOS scaling beyond sub-22 nm node. The multi-gate structure has better short channel behaviors due to enhanced control from the multiple gates. Due to the relatively more mature process and rich learning of the device physics, the FinFET is still extended to 5 nm technology node. In this paper, we proposed a 5 nm FINFET device, which is based on typical 5 nm logic design rules. To achieve the challenging device performance target, which is around 15% speed gain or 25% power reduction against the 7 nm device, we have performed an optimization on the process parameters and iterate through device simulation with the consideration of current process capability. Based on our preferred device architecture, we provide our brief process flow, key dimensions, and simulated device DC/AC performance, like Vt, Idsat, SS, DIBL and parasitic parameters. As a part of the final evaluation, RO simulation result has been checked, which demonstrates that the Performance Per Area (PPA) is close to industry reference 5 nm performance.

Keywords: 5nm FinFET; brief process flow; key dimensions; simulated device DC/AC performance; RO PPA performance